TDR的阻抗誤差、Peeling修正

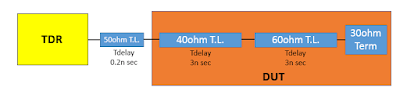

Take-away: TDR 採用step-voltage 當電壓源會有較直觀的阻抗結果 。 TDR 在強烈&多層反射的DUT下,會產生阻抗誤差。 阻抗誤差可用TDR Peeling Algorithm修正。 -----Start 之前介紹過TDR的基本原理 https://sipi-taiwan.blogspot.com/2020/01/tdr.html (如下圖) 當時我們選用step voltage當作source,為什麼呢? 舉例DUT為40ohm + 60ohm + 30ohmTerm。 (如上圖)採用step voltage source在時域上的波型會有明顯的切線,可以輕易的分辨阻抗和時間(傳輸線物理長度)。 (如上圖)採用pulse voltage source,波型亂成一團難以分辨。 NOTE: TDR 使用step-voltage source會有較直觀的阻抗結果。 (如下圖) TDR在有些時候會"失靈",此舉兩例。 case 1: 強烈多重反射,造成TDR阻抗誤差。 DUT為10ohm和50ohm,這麼大的阻抗差會有強烈的反射,使訊號有很長時間/多次的多重反射,造成TDR的誤判。 case 2: 因多層多重反射,離TDR越遠的阻抗誤差越大。 DUT為三段40ohm&60ohm組成,TDR結果顯示第一段40ohm&60ohm尚能準確抓出來,但到了第三段40&60ohm,已經有了誤差。 NOTE: TDR 在強烈&多層反射的DUT下,會產生阻抗誤差。 如何解決多重反射造成的TDR誤差呢? 有個演算法稱為TDR Peeling Algorithm。 Peeling概念為利用不同時間點的阻抗結果來修正誤差的阻抗,筆者在這不詳敘Peeling的推導,僅提供網路文檔資源給讀者參考。 Peeling Doc 1: https://arxiv.org/pdf/1804.00456.pdf Peeling Doc 2: https://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=7342291 NOTE: TDR Peeling Algorit...