別讓GND鋪銅毀了你的訊號

Take-away:

-----Start

- 封裝錫球PAD會有大電容效應,造成走線阻抗下抗,S11變差。

- 在走線旁鋪銅會造成走線阻抗下抗,S11變差。

-----Start

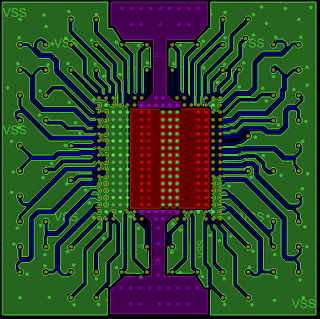

(如下圖)

PCB或者IC Package Desiner在設計完板子後,經常把空白地方鋪滿GND銅。這麼做原因可能為製作上鋪銅率的要求,或者用dynamic shape方便設計造成的結果,或者單純地只是習慣性動作。但在高速訊號上,GND可不能亂鋪! 以下將簡單介紹常見GND帶來的影響、以及改善方法。

(如下圖)

高速差分訊號上,我們會特別設計線寬線距來達到阻抗控制,經由模擬軟體可得知

100歐姆差分對,在此疊構下,線寬23um,線距52um。

我們將此線寬線距套入封裝設計中,最後習慣性地將空白地方撲滿GND銅,圖為BOT和TOP層。

畫好後,我們用3D模擬軟體檢驗封裝電性特性,並畫出S21、S11。

S11約-13.5dB,顯示這不是一個很好的設計。(好的設計通常為-20dB以下)

接著我們用TDR測試觀察阻抗分布,觀察點為封裝BGA處。

可看到設計中充滿低阻抗,此走線設計遠低於我們的目標100歐姆。

我們不是已經控制線寬線距來達到100歐姆了嗎?

為了解謎,我們須進一步『仔細』觀察封裝設計。

為了解謎,我們須進一步『仔細』觀察封裝設計。

(如下圖)

在封裝BOT層,會擺放BGA錫球的PAD(尺寸為550um),且PAD上會有錫球(如下圖箭頭)。

訊號錫球和BOT層的GND,會夾出大面積電容,導致低阻抗。

經過Pad Void改良設計後,我們再做一次模擬。

S11約-23.5dB,比起原本的-13.5dB,改善許多。

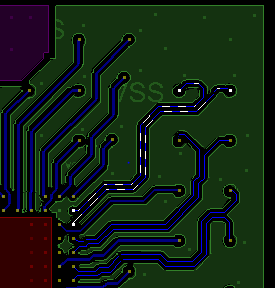

由上圖得知,整體走線還是有低阻抗處,我們更進一步分析原因。

(如下圖)

我們仔細觀察封裝的設計,綠色的GND圍繞在藍色走線的周圍。

在做走線阻抗模擬時,應該將GND一併考慮進來。

(如下圖)

修正模擬結構如下,走線旁加入GND。

得知原本設計的線寬23um/線距52um,其實只有95ohm。

單純地在走線旁鋪銅,就會帶來5ohm的阻抗下降。

S11約-28.6dB,原始設計為-13.5dB,有大幅的進步。

TDR方面,阻抗分布更為平穩,變異量已經小於5%,是個不錯的設計。

NOTE: 在走線旁鋪銅會造成走線阻抗下抗,S11變差。

最後,我們將改善前後的比較列出。

S11由-13.5dB進步到-28.6dB。

S21由-0.46dB進步到-0.21dB。

請注意,我們只是單純的改變GND形狀就會有這麼大的差異,所以在設計PCB/PKG時,可不要再隨性的鋪GND啦~必須嚴謹的模擬和分析,才不會讓GND鋪銅毀了你的訊號

-----END

這應該要修正吧,是影響阻抗,不是毀了信號,阻抗本來就該計算與GND距離

回覆刪除