Power Integrity - PDN時域電壓noise分析

Take-away:

- PDN頻域分析是個很好的分析過程,但最終還是需在時域觀察電壓抖動。

- 時域noise波型可看出頻域Z11共振點頻率。

- 不同Z11 peak表現出不同時域波型,抑制方法也不同。

- 若PDN在f_res有明顯的共振,建議模擬時間至少為1/f_res,才能觀察到最大noise。

上篇中我們看了Power的頻域分析[連結]。

PDN頻域分析是個非常有用的分析過程,但終究還是要回歸到時域。

因為時域上電壓抖動對訊號造成的影響,才是工程師最在意的。

NOTE: PDN頻域分析是個很好的分析過程,但最終還是需在時域觀察電壓抖動。

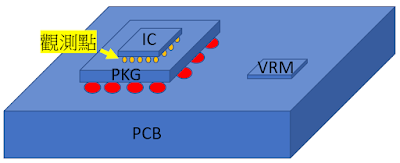

(如下圖)

下圖是頻域分析的PDN Z11,其中有兩個共振點,8MHz & 34MHz。

dV=dI*Z11

若抽載電流dI為寬頻電流,大家能猜到時域電壓noise的波型嗎?

(如下圖) PDN時域noise波型

模擬電路由靜止到全載,抽載一電流0到5A之step current,其中rising time為2ns。

下圖為IC端bump點看到的電壓抖動。

可看出時域noise波型的確主要由8MHz和34MHz形成。

NOTE: 時域noise波型可看出頻域Z11共振點頻率。

(如下圖) PDN時域noise抑制

10ns~50ns為高頻響應,主要由34MHz peak決定。

100ns之後的damping,主要由8MHz peak決定。

若想改善電壓最低值(高一些),那應該減小34MHz的peak,例如之前提過的換一顆ESL小的電容(但因電流為寬頻訊號,所以34MHz和8MHz其實都貢獻不小)。

若想改善電壓damping的強度(較快收斂),那應該減小8MHz的peak,例如之前提過的改善PKG和PCB layout設計。

在此展現出,了解頻域Z11和時域波型的關聯後,再透過頻域Z11分析來找到適當的solution。

這樣的流程比起單純看時域波型找solution,效率大大提升了!

NOTE: 不同Z11 peak表現出不同時域波型,抑制方法也不同。(如下圖) 模擬時間長度

上述的電壓noise波型中,只要模擬25nsec就足以可抓出最大noise。

若有一Z11分布如下,低頻的6.4MHz peak高於高頻peak(常發生於較大的IC電容Cdie)。

若有一Z11分布如下,低頻的6.4MHz peak高於高頻peak(常發生於較大的IC電容Cdie)。

那只模擬到25nsec就足夠抓出最大noise了嗎?

模擬結果如下

若模擬至25ns,量到最大noise為120mv。

若模擬至500ns,量到最大noise為142mv。

若在頻域已觀察到共振f_res,建議模擬時間至少為一個波長1/f_res。

以6.4MHz共振為例,建議至少模擬到1/6.4M=156nsec,才能觀察到最大電壓noise。

NOTE: 若PDN在f_res有明顯的共振,建議模擬時間至少為1/f_res,才能觀察到最大noise。

NOTE: 若PDN在f_res有明顯的共振,建議模擬時間至少為1/f_res,才能觀察到最大noise。

動動腦

上述分析使用了寬頻的current source,電壓noise波型表現和Z11 peak點非常相關。

但若系統採用的是窄頻的current source(例如400MHz電流源),大家可想想電壓noise波型依然和Z11的peak有關係嗎?

-----END

作者已經移除這則留言。

回覆刪除哈囉 版主你好

刪除我是SIPI 的初心手

關於你最後的提問窄頻訊號是否對Z11的PEAK有關係

我認為是有的

因為相對於寬頻電流

I是一直變動(用V=IR的公式來看)

這樣個可以看出Dynamic I 對V的影響(undershoot/overshoot)

不知道這樣理解 是否正確

快兩年了,我想版主應該是想表示窄頻的抽載電流(400MHz的弦波電流),如果這樣看的話通常大於100MHz的電流,都可以由Die上的ODC抑制下來,所以答案是取決於窄頻的頻率,低於100MHz有機會,高於100MHz影響不大。而你提到的因屬於動態抽載電流(Clock的抽載方式),本質上應屬於寬頻電流。只是voltage noise會比版主提到的step wave的方式更嚴重。以上是我的淺見,歡迎指教><

回覆刪除你好,我是SIPI新人,請問是否可以聯係您進行學習指教😀

刪除