為何TDR量測尾巴會往上爬

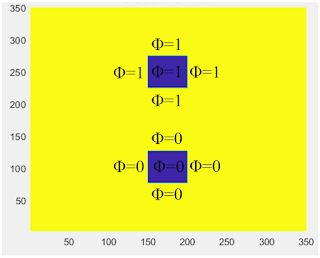

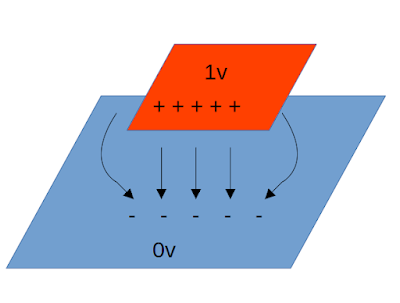

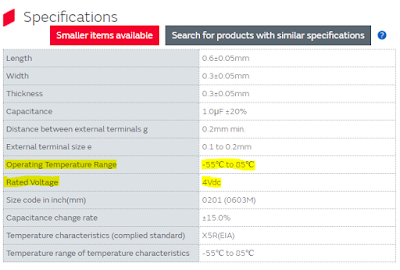

最近同事們討論為何TDR量測尾巴會往上爬。 這是儀器有問題嗎? 其實這是「有損」傳輸線的正常表現。 [阻抗不是恆定值] 大家應該不陌生傳輸線阻抗Z0=sqrt[(R+jwL)/(G+jwC)]。 此公式在電抗>>電阻時,也就是jwL>>R,jwC>>G,簡化為更常用的Z0=sqrt(L/C)。 兩者的差異在於 Z0=sqrt(L/C),阻抗Z0「不隨頻率改變」 Z0=sqrt(R+jwL/G+jwC),阻抗Z0「隨頻率改變」 簡化定性來看 Z0=sqrt(R+jwL/G+jwC)在「極高頻」為Z0=sqrt(L/C) Z0=sqrt(R+jwL/G+jwC)在「極低頻」為Z0=sqrt(R/G),通常會較「大」 如下圖模擬結果,頻率降低,Z0不斷上升。 [TDR為何往上爬] 之前文章中已討論過[ TDR的原理 ], [ 傳輸線模型 ]。 TDR中的電壓源是用step function,而此時域函數乃由寬頻組成。 也就是說,TDR的「高頻」看到了一組Z0值,「低頻」看到了更大的另一組Z0值。 舉例65 ohm的傳輸線 高頻比較快反應,所以先看到了65ohm 接著看到低頻結果,慢慢地65->70->75ohm往上爬 這就是讓TDR量測尾巴往上爬的原因,是有損傳輸線的正常現象。 [控制TDR持平、往上、往下] 有趣的問題來了 TDR只能往上嗎? 可能是平的/甚至往下掉嗎? 理想傳輸線、超導體PEC、超低損介質TDR波型如何呢? 理想傳輸線Ideal T.L. Z0=sqrt(L/C),其中L和C不隨頻率改變,所以低頻時Z0和高頻相同,TDR為定值。 如下圖,阻抗恆定為64.4ohm。 PEC R~0,Z0=sqrt(R/G),所以低頻時Z0幾乎由分母G主導,反而會讓Z0下降。 如下圖,阻抗由63...