我在內層走線量到好大的遠端串擾(FE-XTLK)

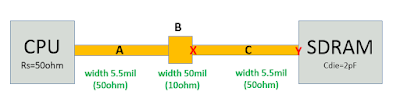

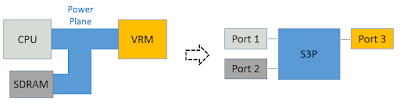

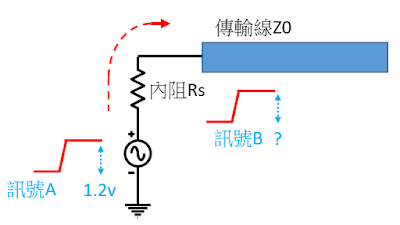

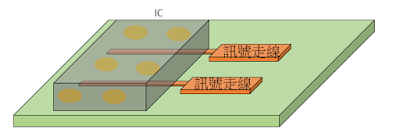

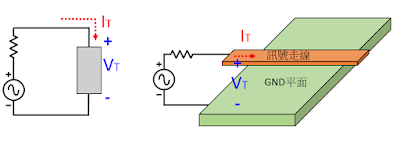

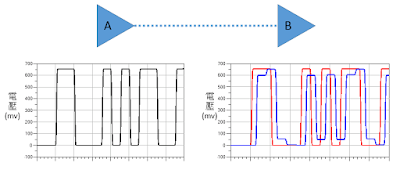

Take-away: 對於訊號傳遞方向而言,內層走線有近端串擾,沒有遠端串擾。 實際PCB設計,訊號受到阻抗不連續產生反射後,此反向傳播訊號會將近端串擾轉變為遠端串擾,讓內層走線也有遠端串擾。 在評估走線要走外層或內層,需考慮完整via數量/via位置/負載型態/走線長度/線距才能準確評估。 -----Start 老闆:這板子要面積小、類比/高速數位訊號、省電不能開ODT,大家有甚麼好建議嗎? 小M:類比最怕高速數位訊號的串擾,我看到書上寫,訊號走內層就完全沒有遠端串擾! 老闆:好!訊號品質絕對是第一優先,那我們就加層數,把訊號由外層移到內層。 (板子製作好回來後‧‧‧) 老闆:小M,為什麼量出來的遠端串擾會這麼大? 內層訊號竟然比外層還髒,你不是說內層訊號沒有遠端串擾嗎? 小M:怎麼會這樣? 沒錯,大部分的SI/PI書籍都寫內層訊號沒有遠端串擾,但相信工程師們在實際的PCB設計上,還是會量到一堆雜訊,這是怎麼一回事呢? (如下圖) 要分析小M的問題,我們先從最單純的架構出發,下圖有一段2200mil(50ohm)傳輸線連接了左邊DR(50ohm)和右邊Term 50ohm,上半部是外層走線的結果、下半部是內層走線。 左上角綠色眼圖是外層走線的近端串擾。 左下角綠色眼圖是內層走線的近端串擾。 >這兩張圖可看出外層和內層都有近端串擾,不同的是外層干擾聚集在rising/falling附近,而內層干擾幾乎是每個時刻都有,這是因為近端串擾會維持2倍走線fly-time,是段很長的時間,所以雜訊很容易就涵蓋了整個bit。這邊我們在乎的是右邊RX接收到的訊號,所以左邊近端串擾的結果影響不大。 右上角綠色眼圖是外層走線的遠端串擾。 右下角綠色眼圖是內層走線的遠端串擾。 >這兩張圖可驗證小M書上的理論是正確的,就是外層有遠端串擾,而內層的遠端串擾幾乎是完美的0。 NOTE: 對於訊號傳遞方向而言,內層走線有近端串擾,沒有遠端串擾。 (如下圖) 接著來看另外一個例子,和上個例子只差在右邊負載不同。下圖是一段2200mil(50ohm)傳輸線連接了左邊DR(50ohm)和右邊Cload (1pF),上半部採用外層走線、下半部採用內層走線。 右上角綠色眼圖是外層走線的遠端串擾...