Power Integrity - 電容MLCC簡介和選擇

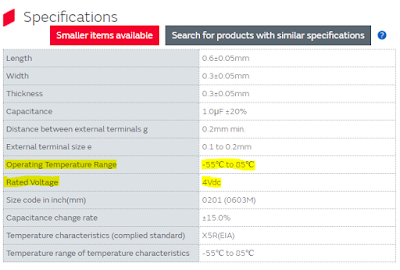

Take-away: MLCC壞掉會短路 ,務必注意 『額定電壓』& 『溫度特性』 。 『 操作DC電壓 』 越接近電容 『額定電壓』,容值越小。 電容尺寸越小,寄生電感越小,但容值上限也小。 高頻(20M~200MHz)可採用小尺寸MLCC電容(0201)、中頻(2M~20MHz)中尺寸MLCC電容(0402)、中低頻(0.1M~2MHz)中大尺寸MLCC電容(0603/0805) 。 -----Start 電容在電路板可做為『高頻率波器』、『訊號bypass路徑』、『電源穩壓』...等 本篇文章簡介『電源穩壓用』之『多層陶瓷電容』MLCC(multi-layer-ceramic-chip),並採用MLCC大廠murata作為範例電容, murata網站連結 。 如何選擇MLCC? 『不能壞』『額定電壓』 某些種類電容壞掉時是開路,只會造成電性效能降低。 但MLCC壞掉是短路,此時已經不是效能差而已,是會對元件造成不可逆的損壞。 所以選擇MLCC第一步就是『不能壞』。 假如電源長時間操作在『95度C』、『5V』,那麼我們選用的電容一定要 MLCC參數中的『額定電壓』一定要大於5V,如選用6.3V or 10V。 MLCC參數中的『溫度特性』高溫範圍一定要大於95C,例如選用X6S or X7R。 『溫度特性』X7R EIA協會定義代號來描述MLCC溫度特性。 例如X7R,第一碼X表低溫至-55度C,第二碼7表高溫至125度C,第三碼R表容值±15%。 例如Y5S,第一碼Y表低溫至-30度C,第二碼5表高溫至85度C,第三碼S表容值±22%。 完整代碼表請見 連結 中的 Table2 。 我們可依據系統操作溫度來選擇對應MLCC,通常越高溫會讓容值下降,造成電性表現變差。MLCC容值變化vs溫度是個非線性關係,例如90度時電容下降5%、100度時電容下降8%。各家電容廠商的溫度vs容值曲線都會不同,但各家廠商能保證的是在操作溫度內,容值變異量要在EIA規範內,例如X7R就是125度C時電容下降要保證在15%內。 『溫度特性』C0G MLCC溫度特性中,代號C0G是個特別的類別(屬於EIA C...