小小的test pad會影響訊號品質? 放哪好?

Take-away:

-----Start

為了保持傳輸線阻抗的連續,我們會盡量讓走線線寬保持一致,但實務上走線中會有無可避免的via pad或test pad,這些pad通常尺寸會比傳輸線來得寬。筆者另一篇文章提過,線寬寬代表電容較大,則阻抗越低。

NOTE: via pad或test pad和傳輸線相比,通常為低阻抗。

C段5000mil,我們可算出訊號需要0.73ns來走完C段。

XY兩端都會反射,訊號首先到達Y後,花了0.73ns由Y到X,被X反射後,又花了0.73ns由X到Y,所以訊號Y->X->Y總共花了約1.5ns。

若觀察SDRAM端Y點的波型,我們預估每1.5ns就會收到一個被彈來彈去的訊號。換句話說,兩端都在反射的架構,共振周期約為走線fly time的2倍。

NOTE: 兩端都在反射的架構,會產生共振,共振周期約為共振路徑fly time的2倍。

(如下圖)

下圖的模擬結果完全符合我們的預期,每1.5ns就會有一個反射波。

(如下圖)

這個出現在訊號中央的反射波絕對不是我們想要的,但透過上述分析,可發現此共振周期和B的長度沒關係,只和C的長度有關係。B的長短不會影響反射波出現的時間點,但會影響反射波深度,這是因為B的左側也會產生新反射,若B很短,則新反射和原本反射會相消。

NOTE: 反射波出現的時間點和test pad長短沒關係,和整體傳輸線架構有關係。

NOTE: 反射波的深度和test pad長短相關。

(如下圖)

如上述分析,SDRAM電容和低阻抗的via/testpad之間的路徑會大大影響共振,所以我們希望此共振路徑越短就好,也就是via/testpad越靠近SDRAM端越好。下圖三者都為總長7200mil的傳輸線,我們將via放在不同的位置,眼圖就會有非常大的不同。若共振路徑很長(如紅色眼圖),那前面bit產生的反射會影響到下好幾個bit,也就是ISI情況嚴重,眼圖就會非常差。反之,若共振路徑很短(如綠色眼圖),那麼訊號品質會好得多。

NOTE: 若SDRAM無termination,且訊號是由CPU送向SDRAM,將testpad放在靠近SDRAM的地方會有較佳的訊號品質。

(如下圖)

對於CPU和SDRAM雙向傳輸的訊號(e.g.DQ/DQS),就無法如上述的方法放置testpad,此時建議使用termination(e.g.ODT)。若我們SDRAM打開ODT後,ODT的反射量比起Cdie小得多,所以via/testpad放置的位置不會影響結果太多(下圖三者眼圖差不多)。另外一個方法是調整testpad和via的形狀(anti pad),提升阻抗來匹配。

-----END

-code_090201

- via pad或test pad和傳輸線相比,通常為低阻抗。

- 兩端都在反射的架構,共振周期約為共振路徑fly time的2倍。

- 反射波出現的時間點和test pad長短沒關係,和整體傳輸線架構有關係。

- 反射波的深度和test pad長短相關。

- 若SDRAM無termination,且訊號是由CPU送向SDRAM,將testpad放在靠近SDRAM的地方會有較佳的訊號品質。

-----Start

為了保持傳輸線阻抗的連續,我們會盡量讓走線線寬保持一致,但實務上走線中會有無可避免的via pad或test pad,這些pad通常尺寸會比傳輸線來得寬。筆者另一篇文章提過,線寬寬代表電容較大,則阻抗越低。

NOTE: via pad或test pad和傳輸線相比,通常為低阻抗。

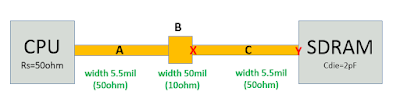

(如下圖)

假設傳訊號由CPU送到SDRAM,走線由A、B、C三段構成,其中B段的線寬較寬但長度短。這時工程師就很常聽到一個問題,B段那麼短對訊號有影響嗎? 筆者這裡可以先預告,B的長短只決定了品質好壞的1/3,對訊號有沒有影響是由CPU、SDRAM、A、B、C共同決定。- 反射@Y:若SDRAM不開ODT,則負載為寄生電容(2pF),可視為高阻抗,所以在Y點會產生很大的正反射。

- 反射@X:C段阻抗50ohm,B段阻抗10ohm,所以在X點會產生很大的負反射。

C段5000mil,我們可算出訊號需要0.73ns來走完C段。

XY兩端都會反射,訊號首先到達Y後,花了0.73ns由Y到X,被X反射後,又花了0.73ns由X到Y,所以訊號Y->X->Y總共花了約1.5ns。

若觀察SDRAM端Y點的波型,我們預估每1.5ns就會收到一個被彈來彈去的訊號。換句話說,兩端都在反射的架構,共振周期約為走線fly time的2倍。

NOTE: 兩端都在反射的架構,會產生共振,共振周期約為共振路徑fly time的2倍。

(如下圖)

下圖的模擬結果完全符合我們的預期,每1.5ns就會有一個反射波。

(如下圖)

這個出現在訊號中央的反射波絕對不是我們想要的,但透過上述分析,可發現此共振周期和B的長度沒關係,只和C的長度有關係。B的長短不會影響反射波出現的時間點,但會影響反射波深度,這是因為B的左側也會產生新反射,若B很短,則新反射和原本反射會相消。

NOTE: 反射波出現的時間點和test pad長短沒關係,和整體傳輸線架構有關係。

NOTE: 反射波的深度和test pad長短相關。

(如下圖)

如上述分析,SDRAM電容和低阻抗的via/testpad之間的路徑會大大影響共振,所以我們希望此共振路徑越短就好,也就是via/testpad越靠近SDRAM端越好。下圖三者都為總長7200mil的傳輸線,我們將via放在不同的位置,眼圖就會有非常大的不同。若共振路徑很長(如紅色眼圖),那前面bit產生的反射會影響到下好幾個bit,也就是ISI情況嚴重,眼圖就會非常差。反之,若共振路徑很短(如綠色眼圖),那麼訊號品質會好得多。

NOTE: 若SDRAM無termination,且訊號是由CPU送向SDRAM,將testpad放在靠近SDRAM的地方會有較佳的訊號品質。

(如下圖)

對於CPU和SDRAM雙向傳輸的訊號(e.g.DQ/DQS),就無法如上述的方法放置testpad,此時建議使用termination(e.g.ODT)。若我們SDRAM打開ODT後,ODT的反射量比起Cdie小得多,所以via/testpad放置的位置不會影響結果太多(下圖三者眼圖差不多)。另外一個方法是調整testpad和via的形狀(anti pad),提升阻抗來匹配。

-code_090201

反射點Y 應該是低阻抗https://www.gstatic.com/images/icons/material/system/1x/close_black_24dp.png

回覆刪除