Power Integrity - PDN頻域Z參數解析

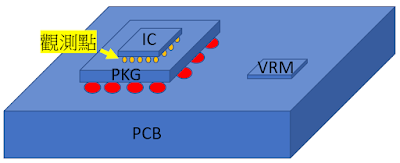

Take-away: 常用「IC pad/bump點的頻域Z參數」當作PI分析參數 PDN Z參數不能只能看共振點,各段都要仔細分析。 改善PDN共振點,需知道共振點的成因,找出共振點對應的LC 。 拼命加電容不一定能改善PDN,要確切知道問題點才有效。 -----Start Power的穩定性是工程師的一大挑戰,往往可能比signal更令人頭疼。 一般人常認為power的特性難以估計、千變萬化,只能拼命加電容。 但其實仔細觀察、一步一步的拆解、抓住關鍵參數,還是有跡可循的喔! 筆者將介紹PDN頻域分布、時域波型、layout設計、電容選擇、電流抽載...等。 本篇由PDN頻域開始! (如下圖) 觀測點 & Z參數 歐姆定律dV=dI*Z, 其中 dI為IC電路抽載電流,由內部電路決定。 dV為電壓變動,目標是電壓變動越小越好。 Z參數為PDN阻抗分布,是 dV/dI兩者橋梁。 我們要穩壓的點是IC內部,所以我們常用「IC pad/bump點的頻域Z參數」當作PI分析參數。 NOTE: 常用「IC pad/bump點的Z參數」當作PI分析參數 (如下圖) PDN頻譜分布 以下為 IC pad/bump點的PDN Z阻抗結果,阻抗值隨頻率不同。 可以看到PDN有兩個共振點,分別在8MHz和34MHz。 大部分的Z參數也是類似此圖,有2~3個共振點。 我們仔細的分析PDN Z參數, 將其拆成五段A、B 、C、D、E。 由Z參數的斜率,可知道ACE為電容性,BD為電感性。 A: Die內部電容。 B: Pad/bump到封裝電容的路徑電感 + 封裝電容的寄生電感。 C: 封裝電容。 D: Pad/bump到PCB電容的路徑電感 + PCB電容的寄生電感。 E: PCB電容。 共振點P1主要由A、B構成。 共振點P2主要由C、D構成。 NOTE: PDN Z參數不能只能...