IC封裝高速訊號的關鍵:PTH Via過孔

Take-away:

- 使用TDR觀測阻抗時,需依照頻寬需求調整TDR risetime。

- 長PTH在高頻上為高阻抗。

- 降低PTH阻抗方法有拉近P/N PTH、放置GND PTH在差分訊號周圍。

- 高速訊號上,PTH/BGA是一大關鍵,務必降低阻抗不連續。

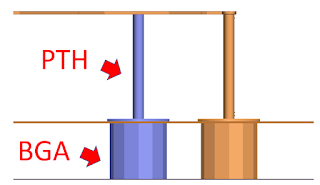

在IC封裝設計,CORE層相比PP層厚上許多,常見CORE層厚度為500/800/1200um,PP層厚度為20-35um。用於CORE層的過孔VIA為機鑽孔,又稱為PTH,而用於PP層為雷射孔。

(如下圖)

PTH在整體PKG設計中,影響電性效果很多,原因如下。

- PTH為非均勻傳輸線(non-uniform transmission line),沒有一個固定的阻抗值。

- PTH長度不短(500um-1200um)。

- PTH和走線架構差異大,交界處會有不連續效應。

(如下圖)

筆者之前文章已探討過BGA的阻抗特性:別讓GND鋪銅毀了你的訊號

那麼PTH阻抗特性為何呢? 這裡用TDR模擬來一探究竟。

舉800um的PTH為例,下圖為一對差分訊號TDR結果分布,觀測點為BGA。

阻抗結果顯示211ps低阻抗95ohm,225ps高阻抗105ohm。

此結果「似乎」不差,在100ohm的正負5%內。

(如下圖)

這時候有經驗的工程師一定會問

「目標訊號多快? 此模擬TDR rise time多少?」

沒錯,若我們目標是56Gbps NRZ,那麼50ps rise time的TDR是完全不夠的,速度太慢看不到高頻的反應。(50ps的TDR適用於約16Gbps NRZ)

所以我們將TDR rise time調整為更快的15ps,觀測點為BGA。

阻抗結果顯示207ps低阻抗87ohm,225ps高阻抗112ohm。

此時阻抗偏離100ohm已經超過10%。

TDR結果中,

207ps低阻抗87ohm為BGA結構對PKG GND Plane / GND Ball / PCB GND plane夾出的大電容。

225ps高阻抗112ohm為PTH結構中段的電感效應,此時PTH中段離上層GND plane已達400um。

NOTE: 使用TDR觀測阻抗時,需依照頻寬需求調整TDR risetime。

(如下圖)

PTH中段為高阻抗架構,長度越長時會更明顯。

常見降低PTH阻抗方法有

- 將差分訊號的P&N PTH靠近些。

- 放置GND PTH在差分訊號周圍。

下面範例為把P/N PTH距離由800um拉近到300um.

TDR結果顯示,阻抗由112降至93ohm。

NOTE: 長PTH在高頻上為高阻抗。

NOTE: 降低PTH阻抗方法有拉近P/N PTH、放置GND PTH在差分訊號周圍。

封裝PTH和BGA形成的高低阻抗落差,會對高頻訊號造成很大的影響。

在中低速訊號時(小於25Gbps)時影響可能不大,但到了56Gbps時,PTH、BGA結構都需照封裝架構來特別最佳化,才有可能在S11達標。

(有機會再介紹如何設計高達112Gbps的PAM4訊號)

NOTE: 高速訊號上,PTH/BGA是一大關鍵,務必降低阻抗不連續。

-----END

留言

張貼留言