Power Integrity - PDN時域電壓noise分析

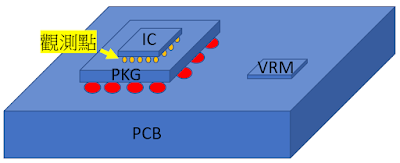

Take-away: PDN頻域分析是個很好的分析過程,但最終還是需在時域觀察電壓抖動。 時域noise波型可看出頻域Z11共振點頻率 。 不同Z11 peak表現出不同時域波型,抑制方法也不同 。 若PDN在 f_res有明顯的共振,建議 模擬時間至少為 1/f_res,才能觀察到最大noise。 -----Start 上篇中我們看了Power的頻域分析[ 連結 ]。 PDN頻域分析是個非常有用的分析過程,但終究還是要回歸到時域。 因為時域上電壓抖動對訊號造成的影響,才是工程師最在意的。 NOTE: PDN頻域分析是個很好的分析過程,但最終還是需在時域 觀察 電壓抖動。 (如下圖) 下圖是頻域分析的PDN Z11,其中有兩個共振點,8MHz & 34MHz。 dV=dI*Z11 若抽載電流dI為寬頻電流,大家能猜到時域電壓noise的波型嗎? (如下圖) PDN時域noise波型 模擬電路由靜止到全載,抽載一電流0到5A之step current,其中rising time為2ns。 下圖為IC端bump點看到的電壓抖動。 可看出時域noise波型的確主要由8MHz和34MHz形成。 NOTE: 時域noise波型可看出頻域Z11共振點頻率。 (如下圖) PDN時域noise抑制 10ns~50ns為高頻響應,主要由34MHz peak決定。 100ns之後的damping,主要由8MHz peak決定。 若想改善電壓最低值(高一些),那應該減小34MHz的peak,例如之前提過的換一顆ESL小的電容(但因電流為寬頻訊號,所以34MHz和8MHz其實都貢獻不小)。 若想改善電壓damping的強度(較快收斂),那應該減小8MHz的peak,例如之前提過的改善PKG和PCB layout設計。 在此展現出,了解頻域Z11和時域波型的關聯後,再透過頻域Z11分析來找到適當的solution。 這樣的流程比起單純看時域波型找solution,效率大大提升了! NOTE: 不同Z11 peak表現出不同時域波型,抑制方法也不同 。 (如下圖) 模擬時間長度 上述的電壓noise波型中,只要模擬25nsec就足以可抓出最大noise。 若有一Z11分布如下,低頻的6.4MHz peak高於...