Cadence Sigrity模擬自動化(TCL)

-----Start

因為工作實在太忙碌了,上次更新此網站是一年半前了。

趁著聖誕假期,外國人休假去了,很開心可以再聊聊SI/PI。

一個PKG/PCB設計,從前期參數設計,post-layout電性驗證sign-off,完工後的debug。

這些都倚賴模擬來分析,可想像模擬的量只會越來越多。

以往1~2個模擬案件,工程師有機會純手動完成。

但若老闆要求做100個、甚至1000個模擬呢? 想必純手動非常困難了。

此篇介紹Cadence Sigrity系列自動化操作。

先前文章介紹過Cadence PowerSI,本文仍用PowerSI當作範例。

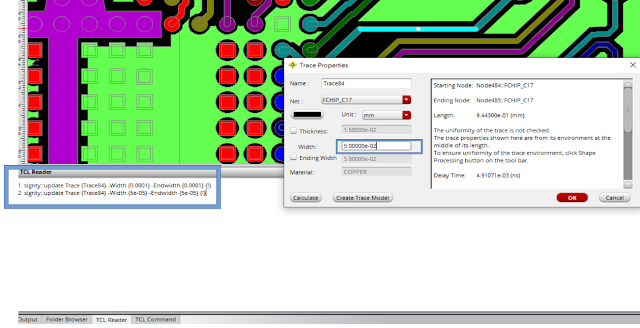

(如下圖) TCL編輯器

PowerSI切換至TCL Command window。

TCL就是一種程式語言,指令分為兩種

通用TCL command

Sigrity專用TCL command

(如下圖) 通用TCL command

通用指令可至TCL基本指令查詢。

例如:HelloWorld(可複製貼上)

set test "hello world"

puts $test

執行結果

當然TCL語法也支持if, loop, for, array, logic...等各種基本語法。

例如:用for迴圈設定寬度1mm到9mm(可複製貼上)

for {set ii 1} {$ii<10} {incr ii 2} {

set TraceWidth $ii

puts TraceWidth={$TraceWidth}mm

}

執行結果

(如下圖) Sigrity專用TCL command

若想用TCL控制PowerSI的選項,例如設定線寬,該怎麼做呢?

Cadence提供非常好用的「TCL錄製功能」,可直接將使用者操作翻譯成TCL。

先點選上方「Record TCL」,再點選「Show current TCL script」。

之後,使用者在PowerSI做的任何操作,都會被紀錄且翻譯成TCL啦~

sigrity::update Trace {Trace84} -Width {0.0001} -Endwidth {0.0001} {!}

是不是很方便呢? 使用者甚至不需要查詢指令手冊,PowerSI已經自動幫我們打出來了。

這些Sigrity專用的的TCL command,指令開頭都會有sigrity::,且結尾為{!}因為是PowerSI下錄製的TCL,不見得PowerDC能通用。

(如下圖) 通用TCL command + Sigrity專用TCL command

聰明的你,應該已想到更進階的使用了吧

通用的TCL,再配上Sigrity專用TCL command,就可以自動化非常多事情啦!

例如:更改線寬由1mm到9mm,每次更改就儲存成一個獨立SPD file(可複製貼上)

for {set ii 1} {$ii<11} {incr ii 2} {

#打開檔案

sigrity::open document {D:/1.spd} {!}

#設定線寬參數

set TraceWidth [expr double($ii)*1e-5]

#更改線寬

sigrity::update Trace {Trace84} -Width $TraceWidth -Endwidth $TraceWidth {!}

#存檔spd

set fileName "D:\\$ii.spd"

sigrity::save $fileName

}

有了TCL,可以輕易幾秒內完成5個SPD的設定了

是不是很方便呢?

(如下圖) 背景執行PowerSI + TCL

我們已經把操作指令化了。

接著我們把整個PowerSI都指令化,背景直接執行TCL。

先將上述介紹的TCL指令儲存成D:\test.tcl

並在cmd命令提示字元下輸入: powersi -b -t D:\test.tcl

powersi就會在背景執行TCL,不彈出任何powersi視窗。

至此

我們完成了在背景運行powersi,執行tcl,完成設定自動生成5個SPD,分別代表不同線寬參數。

-----END

留言

張貼留言